・2022/06/25

FPGA Spartan-6 XC6SLX16でファミコンを動かす!

FPGA Spartan-6 XC6SLX16でファミコンを動かす!

(Xilinx FPGA Spartan-6 XC6SLX16 NES clone in ALINX AX309)

Tags: [FPGA], [電子工作], [Xilinx XC6SLX9], [FPGA 2022]

● FPGA Spartan-6 XC6SLX16でファミコンを動かす!

Xilinx FPGA Spartan-6 XC6SLX16 NES clone in ALINX AX309

fpga_nes

オリジナルの Digilent Nexys 3版の fpga_nes

元が Digilent Nexys 3の基板を使っていますが、使っている FPGAは私の購入した AX309 cloneと同じ XC6SLX16を使用しています。

[AX309] XILINX Spartan-6 XC6SLX9 FPGA Development Board LX9 - Spartan6 - ALINX Electronics Technology (Shanghai) Co., Ltd.

alinxalinx / AX309

Digilent Nexys 3 Spartan-6 FPGA board

● Digilent Nexys 3基板と ALINX AX309基板との違いに対応する

Digilent Nexys 3基板と ALINX AX309基板との違いは下記の 3箇所です。

a) 入力クロックの周波数(Nexys 3基板は 100MHz、AX309基板は 50MHz)

b) I/O部分のピン配置(基板配線が異なるから)

c) ボタン入力の論理(Nexys 3基板は正論理、AX309基板は負論理)

・ a) 入力クロックの周波数

入力クロックの周波数の違いは Nexys 3は 100MHz、AX309 cloneは 50MHzなので

a) 内部の回路実装のクロック分周を半分にする

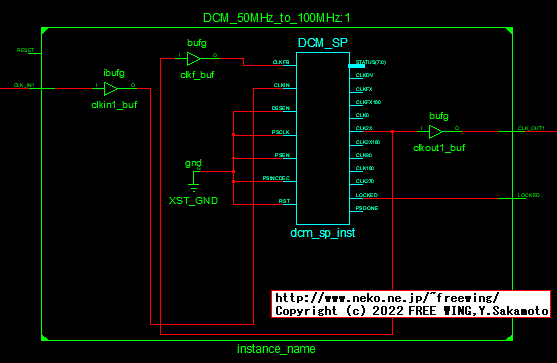

b) FPGAの DCMの機能を使って 50MHzを 100MHzにする

のそれぞれの修正で対応できましたが、(a)のクロック分周の箇所は複数有るので (b)の方法が手軽で簡単です。

Digital Clock Manager (DCM) Module

DCM = 簡単に言うと好きな周波数を指定して出力できるモジュール。

Spartan-6でも使えます。

・ b) I/O部分のピン配置(基板配線が異なるから)

I/O部分のピン配置の違いは .ucfファイルのピン定義の書き換えで対応しました。

UCF = User Constraints Fileの略で、FPGAの回路を FPGAのどのピンに割り当てるか?クロックのタイミング等を記述するファイル。

Constraints Guide

UG625 (v. 13.4) January 18, 2012

ちなみに新しい開発ツール Vivaoの場合は XDCと言い、ISEの UCFとは記述方法が異なる。

ISE to Vivado Design Suite Migration Guide

ISE から Vivado Design Suite への移行ガイド

重要: デザインにタイミング制約または物理制約を適用するには、 UCFをザイリンクス デザイン制約 (XDC) フォーマットに変換する必要があります。

XDC = Xilinx Design Constraintsの略、Vivado Design Suiteで使う。従来の ISEの UCFに相当する。

・ c) ボタン入力の論理(Nexys 3基板は正論理、AX309基板は負論理)

topレベルのデザインに論理反転の記述を追加しました。

・Digilent Nexys 3基板と ALINX AX309基板との違いに対応する

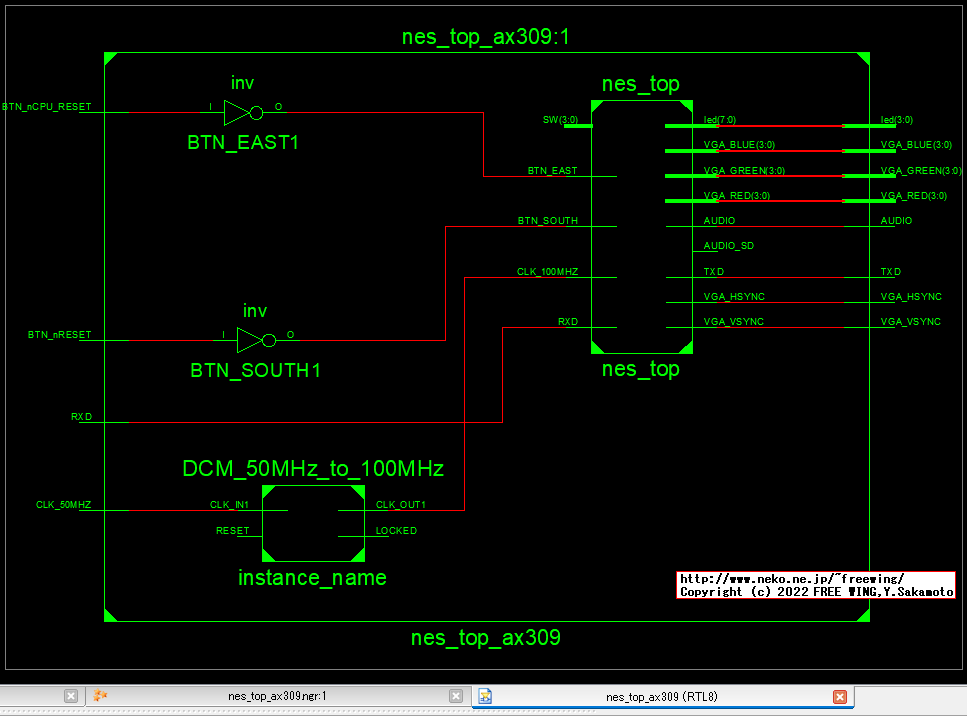

fpga_nesの AX309版のブロック図。

topレベルのデザインに 100MHz生成の DCMとボタン入力の論理反転を追加しました。

FPGAの DCMの機能を使って 50MHzを 100MHzにする

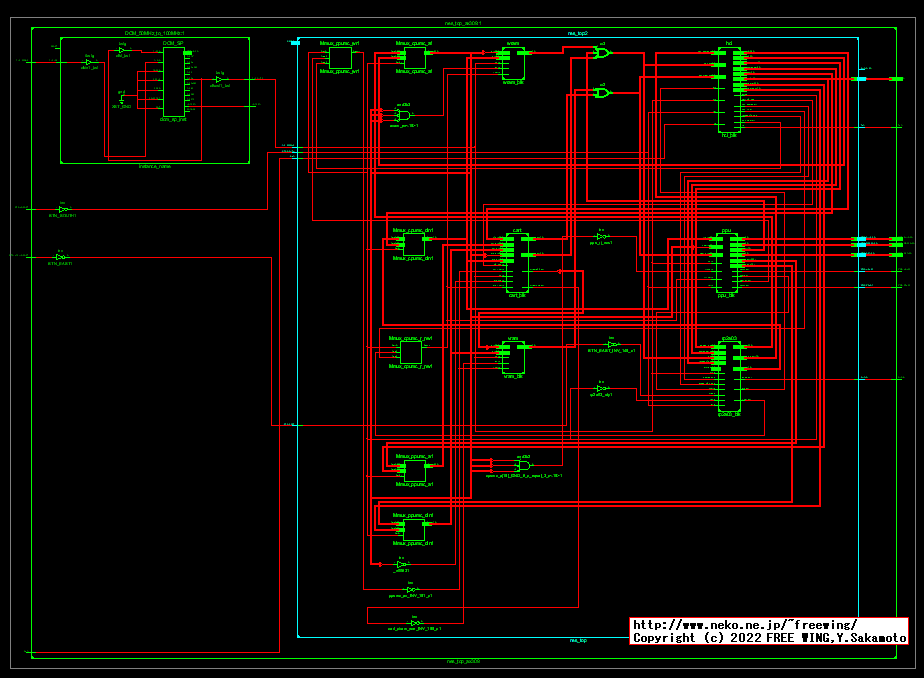

潰れて見えませんが fpga_nesの内部の構成。

● Nexys 3 Spartan-6 FPGA board用の実装を ALINX AX309 cloneで動く様に改変したもの

Development Environment

・ISE 14.7 WebPack (free)

・Visual Studio 2017 Community (free)

・ALINX AX309 clone Xilinx FPGA Spartan-6 XC6SLX16

FREEWING-JP/fpga_nes

Nexys 3 Spartan-6 FPGA board用の実装を ALINX AX309 cloneで動く様に改変した fpga_nes

オリジナルの https://github.com/brianbennett/fpga_nes に

brianbennett#34

の

denghongcai@021a890のパッチ

を適用しています。

・オリジナルの https://github.com/brianbennett/fpga_nes

・Windowsパソコンと FPGAとの UART通信が 38400bps

・本物のファミコンのコントローラを FPGAの I/Oに接続する

・RGB出力が 256色(RGB332)

[Windows PC] nesdbg.exe -- (38400bps) -- [Nexys 3 Spartan-6 FPGA board] -- VGA display (RGB332,640x480,31KHz)

+-- [actual NES Controller(4021 shift register)]

・ denghongcai改造版 https://github.com/denghongcai/fpga_nes

・Windowsパソコンと FPGAとの UART通信が高速化 256000bps

・Windowsパソコンに USBジョイパッドを接続して FPGAに通信で転送

・RGB出力が 4096色(RGB444)

[Windows PC] nesdbg.exe -- (256000bps) -- [Nexys 3 Spartan-6 FPGA board] -- VGA display (RGB444,640x480,31KHz)

+-- USB joypad

・ FREE WING改造版 https://github.com/FREEWING-JP/fpga_nes

単純に denghongcai改造版を AX309で動く様にした

制限事項:音が非常にノイジー

[Windows PC] nesdbg.exe -- (256000bps) -- [ALINX AX309 clone Spartan-6 FPGA board] -- VGA display (RGB444,640x480,31KHz)

+-- USB joypad

● fpga_nesの FPGAに USB HIDの GAMEPADを接続してコントローラとする事に成功

USB GAMEPADを FPGAに接続します。

[Windows PC] nesdbg.exe -- (256000bps) -- [ALINX AX309 clone Spartan-6 FPGA board] -- VGA display (RGB444,640x480,31KHz)

+-- USB joypad

GitHubにプロジェクトをアップロードしています。

https://github.com/FREEWING-JP/fpga_nes/tree/feature/support_usb_gamepad

下記の「なんちゃって FPGA USB HOST」を fpga_nesに組み込んで、FPGAに直接 USBデバイスを接続してゲームコントローラとする事に成功しました!!

・2022/07/23

USB HOST機能を FPGAに実装する方法、FPGAの GPIOに USB HIDデバイスを接続したい!!

FPGAに USB HOST機能を実装して Low Speedの USB HIDデバイスを接続するのら

● FPGA NESにファミカセのゲーム イメージ .nesファイルを転送する方法

ファミカセのイメージ(.NESファイル)は USBのシリアル COM portでパソコンから転送します。(Visual Studioで作成した C++のアプリ nesdbg.exeを使用する)

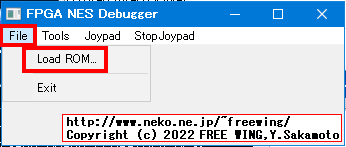

1) nesdbg.exeを COM port番号を指定して起動する。

2) Fileメニューの Load ROM...を選択して .nesファイルを転送する。

rem 123 as COM port COM123

nesdbg.exe 123

rem Select File and Load ROM...

・FPGA NESにファミカセのゲーム イメージ .nesファイルを転送する方法

● fpga_nesは Mapper 0だけの対応です。("Only mapper 0 is supported.")

Mapper 0 = プログラム領域 16/32KB、キャラクタ定義 8KB

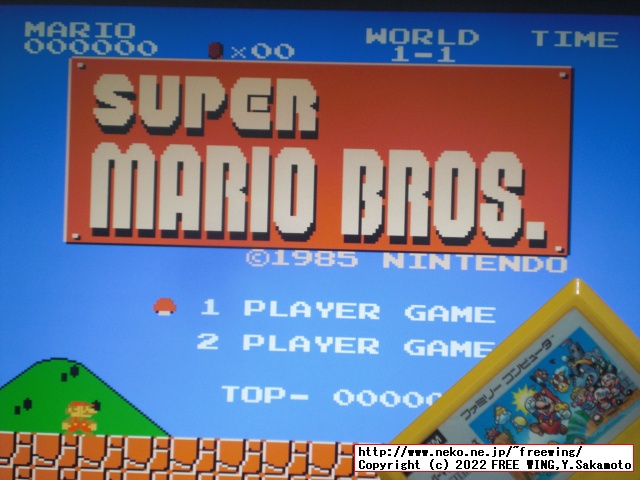

と言う訳でファミコンと言えば当時爆発的大ヒットのスーパー マリオ ブラザーズ。

スーパー マリオ ブラザーズが動くと言う事は Mapper 0を使ってる…ってコト!?

スーパー マリオ ブラザーズのプログラムサイズって 32KBで済んでいるの?凄い!

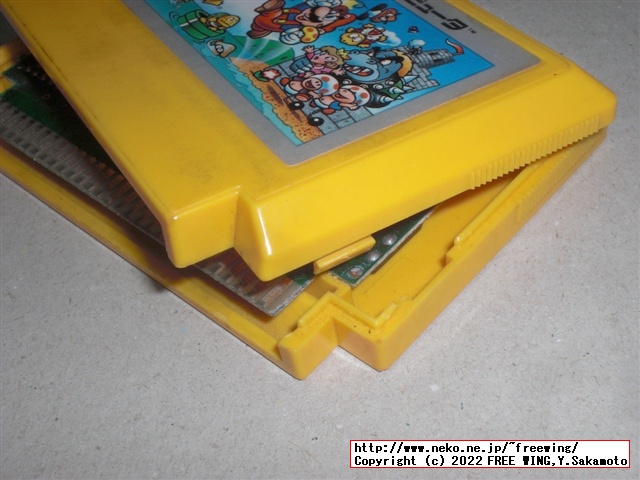

・AX309 clone XC6SLX16とファミカセ

・Spartan-6 XC6SLX16で fpga_nesでスーパー マリオ ブラザーズを動かした所

任天堂の公式のスーパーマリオブラザーズのマニュアル PDF

https://www.nintendo.co.jp/clv/manuals/ja/pdf/CLV-P-HAAAJ.pdf

● HVC-SM SUPER MARIO BROS. NES Cassette teardown PCB

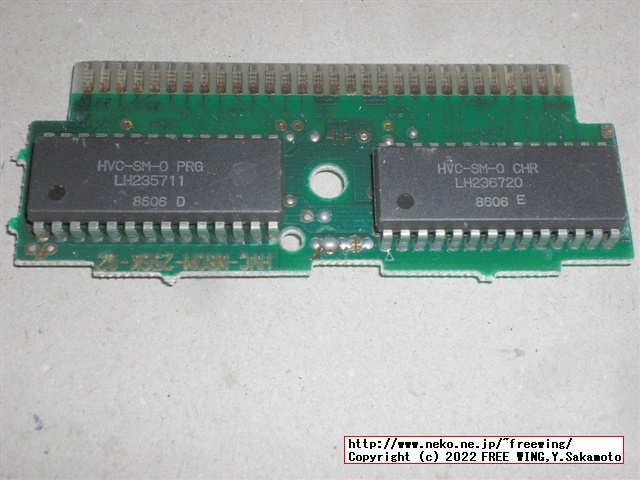

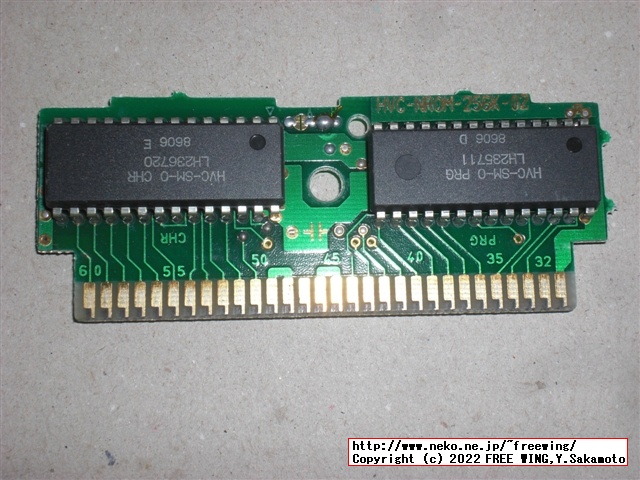

これが日本中(世界も)を熱狂させたゲームの正体!

プログラムとキャラクタの合計で 40KB!!!

40KBと言うサイズは 1GBの 26214分の 1の容量です!!

1MBの場合は 26分の 1の容量です!!

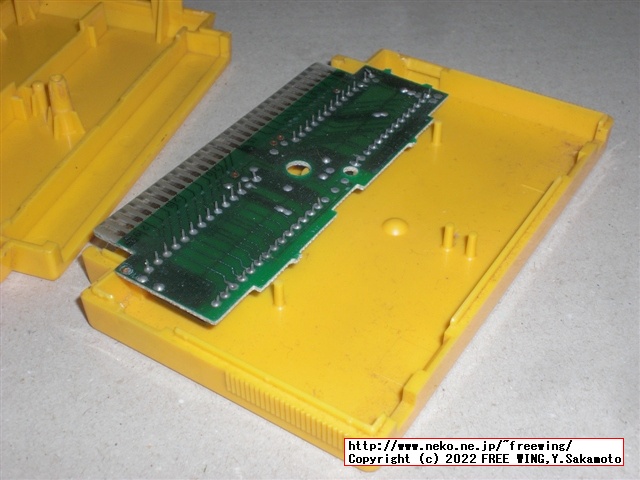

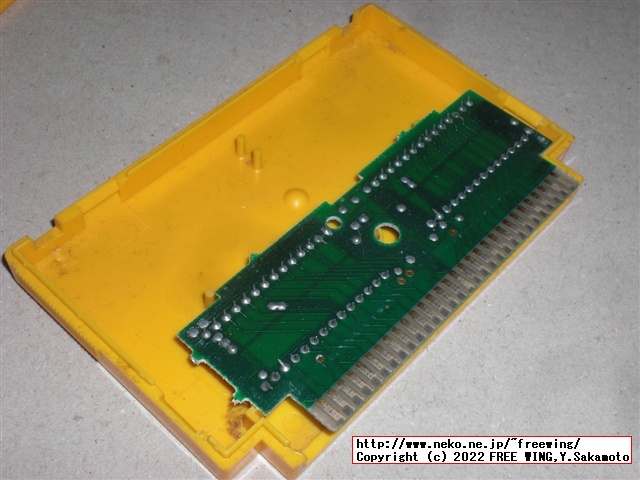

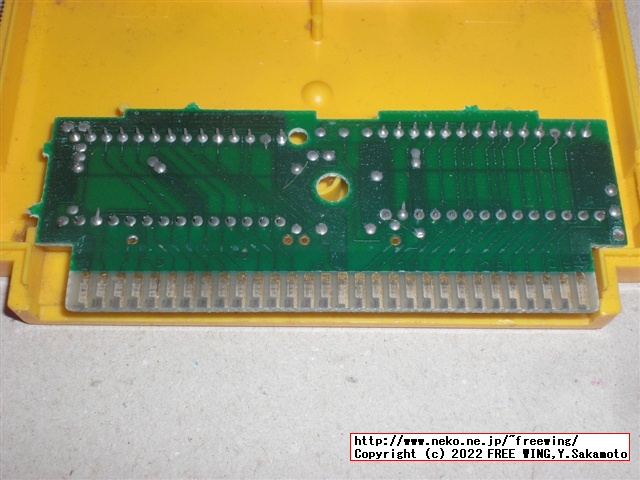

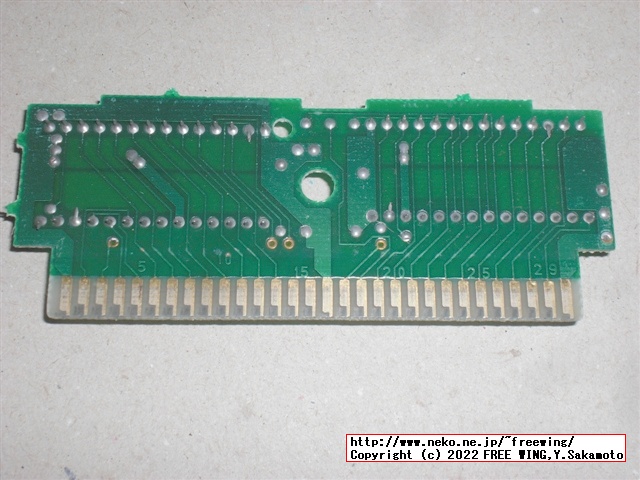

・スーパー マリオ ブラザーズのファミカセの中身の基板

HVC-SM-0 PRG LH235711 8606 D プログラムの 32KB ROM

HVC-SM-0 CHR LH236720 8606 D キャラクタの 8KB ROM

LHと言えば SHARPの型番ですね!

後期ロットは ROMがボンディング(黒丸)になっているらしい。

・スーパー マリオ ブラザーズのファミカセの中身の基板

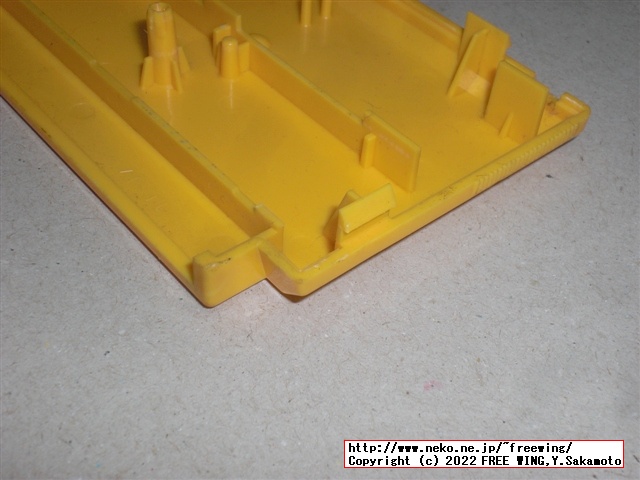

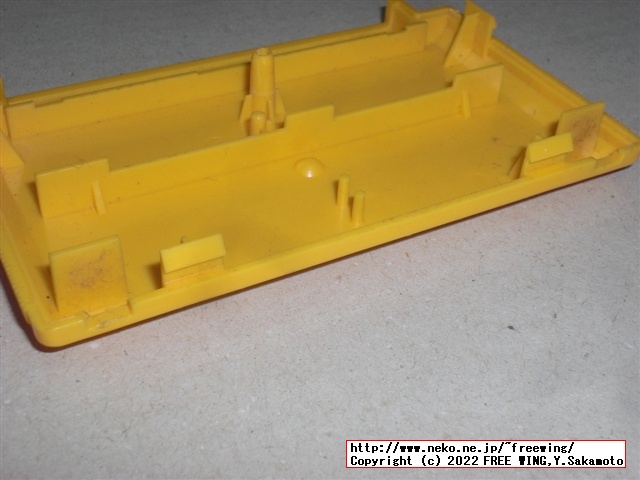

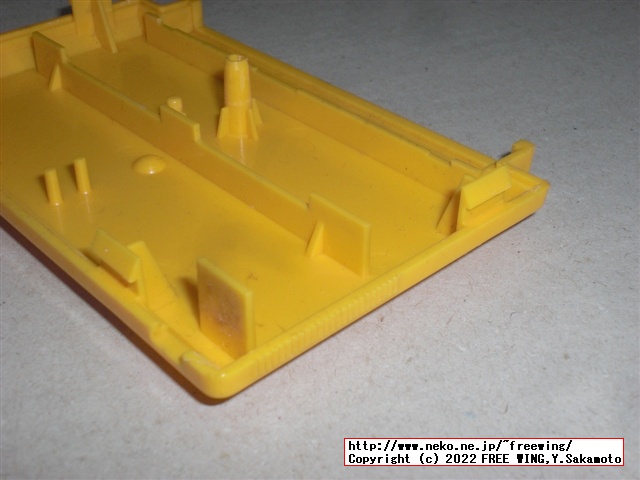

●ファミカセの爪を折らないで分解する方法

カートリッジの差し込み部分の左側の所を手で少し広げて隙間を作る。

マイナスドライバーを差し込み、カセットの表面側にドライバーを起こす。

カセット下部の脇の爪が外れる。

同様に反対の右側の爪を外す。

カセット上部の左側の空気穴にマイナスドライバーを差し込む。

カセットの表面側にドライバーを起こす。

カセット上部の右側の空気穴にマイナスドライバーを差し込む。

カセットの表面側にドライバーを起こす。

以上。

なお、マイナスドライバー(金属)だとカセットのプラスチック側に微妙に凹みが出来ると思って、クレジットカードで試しましたが、強度的にクレジットカードの方が負けました。

●その他

重大度レベル コード 説明 プロジェクト ファイル 行 抑制状態

エラー LNK2019 未解決の外部シンボル __imp__joyGetPosEx@8 が関数 "public: void __thiscall ThreadX::ThreadEntryPoint(void)" (?ThreadEntryPoint@ThreadX@@QAEXXZ) で参照されました。 nesdbg nesdbg.obj 1

#pragma comment(lib, "winmm.lib")

add Winmm.lib to lib

Tags: [FPGA], [電子工作], [Xilinx XC6SLX9], [FPGA 2022]

●関連するコンテンツ(この記事を読んだ人は、次の記事も読んでいます)

AMD Xilinxの FPGA Spartan-6 XC6SLX16のボードを買ってアーケード ゲームを動かす

ALINX AX309 XC6SLX9の中華クローンの XC6SLX16版を購入しました

AMD Xilinxの FPGAの開発アプリ ISE WebPackをダウンロードして Windows 10で動かす方法

Spartan-6の FPGAの開発用に Xilinx ISE WebPack開発ソフトウェアを Windows 10で動かす方法

Xilinxの FPGA Spartan-6の Block RAM RAMB8BWERに初期値を入れて ROMとして使う方法

Xilinxの FPGA Spartan-6の Block RAM RAMB8BWERに初期値を入れて ROMとして使う方法

Xilinxの FPGA Spartan-6で PicoBlaze KCPSM 8 ビット マイクロコントローラーを動かす!

PicoBlaze KCPSM6 in Spartan-6 with ISE WebPack

Xilinxの FPGA Spartan-6で MicroBlazeを ISE WebPack 14.7で無料ライセンスで動かす方法

How to MicroBlaze in Spartan-6 with ISE WebPack 14.7 only Free License to Blink LED !

USB HOST機能を FPGAに実装する方法、FPGAの GPIOに USB HIDデバイスを接続したい!!

FPGAに USB HOST機能を実装して Low Speedの USB HIDデバイスを接続するのら

USBの通信プロトコルを勉強する

今まで漠然としていた USBデバイスの通信方法を理解します

USB HOST機能が欲しいのでワンチップマイコンの GPIOで USB HOST機能を実現する

FPGAに USBデバイスを接続したいのですが、USB HOSTの通信を実装できないので困っています

OLIMEX LPC-H40(Philips LPC2106)

MOTHER BOARD for LPC-H40(LPC-H2106) and ASM Sample Program.

線形帰還シフトレジスタ LFSRのまとめ、FPGAの Verilog HDLでの実装例

LFSR Linear Feedback Shift Registerについて調べた

【2022年版】最近流行の RISC-Vプロセッサの環境を WSL Ubuntu上に構築する方法

RISC-Vプロセッサの Rocket Chipの開発環境を Windows上に構築して Verilogする方法

XILINX FPGAのBlock RAMをROMとして使う方法

FPGAに内蔵のBLOCK-RAMにROMとして初期値を与える方法

スパルタン2で"ギャラクシアン基板"を作る!

Verilog言語で記述してあります

スパルタン2で"MIDWAY 8080(TAITO インベーダ基板)"を動かす!

ハードウェアで本物を作ります

スパルタン2で"パックマン"を動かす!

FPGAでパックマンが動きます

スパルタン2で"ド*キーコ*グ"を動かす!

これもFPGAで動いちゃいます

スパルタン3でアーケードゲームを動かす!

XAPP694の使用例、INVADER/GALAXIAN/PACMAN/D*NKEY-K*NG/TIME PILOT

[HOME]

|

[BACK]

リンクフリー(連絡不要、ただしトップページ以外は Web構成の変更で移動する場合があります)

Copyright (c)

2022 FREE WING,Y.Sakamoto

Powered by 猫屋敷工房 & HTML Generator

http://www.neko.ne.jp/~freewing/fpga/xilinx_spartan_6_nes_ax309/