・2022/07/01

Xilinxの FPGA Spartan-6で PicoBlaze KCPSM 8 ビット マイクロコントローラーを動かす!

Xilinxの FPGA Spartan-6で PicoBlaze KCPSM 8 ビット マイクロコントローラーを動かす!

(PicoBlaze KCPSM6 in Spartan-6 with ISE WebPack)

Tags: [FPGA], [電子工作], [Xilinx XC6SLX9], [FPGA 2022]

● Xilinxの FPGA Spartan-6で PicoBlaze 8 ビット マイクロコントローラーを動かす!

PicoBlaze KCPSM6 in Spartan-6 with ISE WebPack

PicoBlaze 8 ビット マイクロコントローラー

Release 9 of KCPSM6 (What’s new?)

KCPSM6 is Here! (Download it now)

● Xilinxの KCPSM PicoBlaze 8-bit Microcontrollerをダウンロードする方法

How to Download Xilinx KCPSM PicoBlaze 8-bit Microcontroller

・Xilinx PicoBlaze KCPSM6 Download KCPSM6_Release9_30Sept14.zip

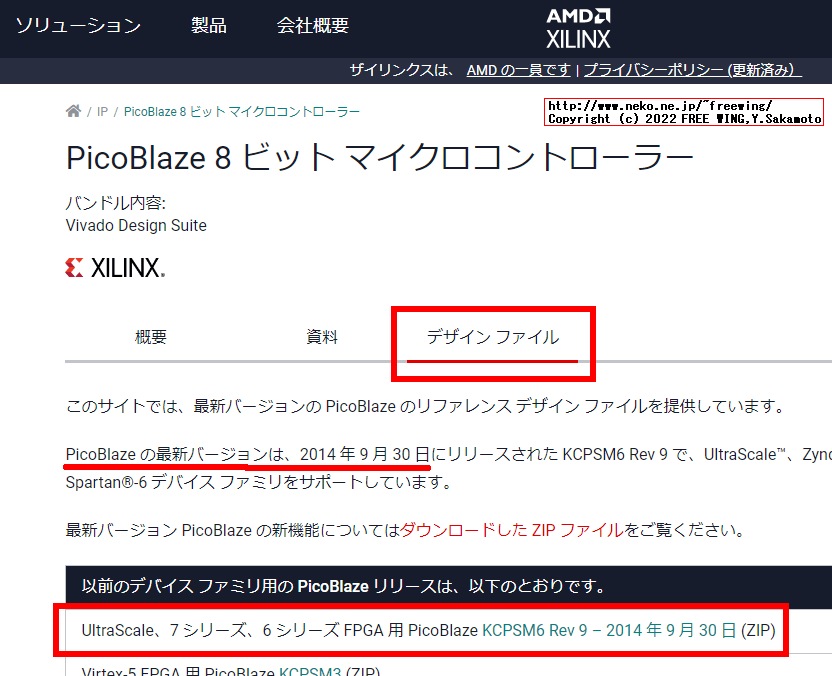

デザインファイルの所から

UltraScale、7 シリーズ、6 シリーズ FPGA 用 PicoBlaze KCPSM6 Rev 9 - 2014 年 9 月 30 日 (ZIP)

KCPSM6_Release9_30Sept14.zip

をダウンロードします。

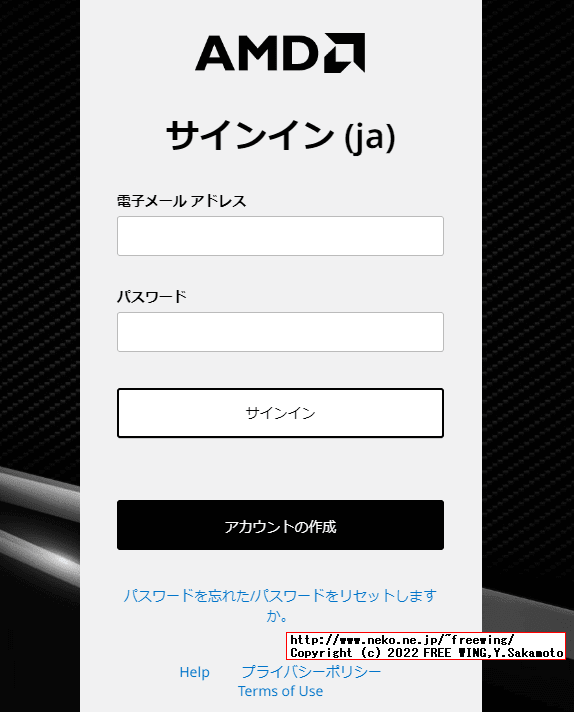

ログインします。

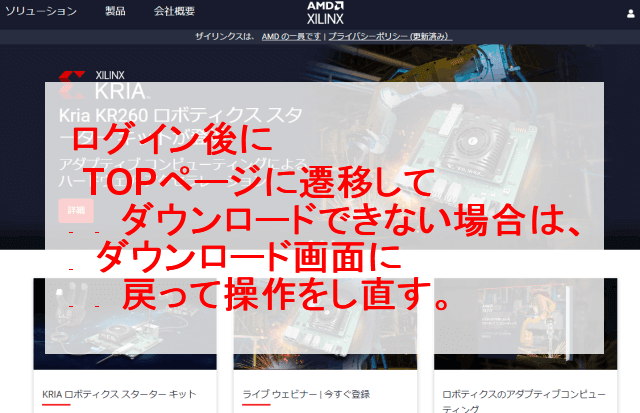

ログイン後に TOPページに遷移してダウンロードできない場合は、ダウンロード画面に戻って操作をし直す。

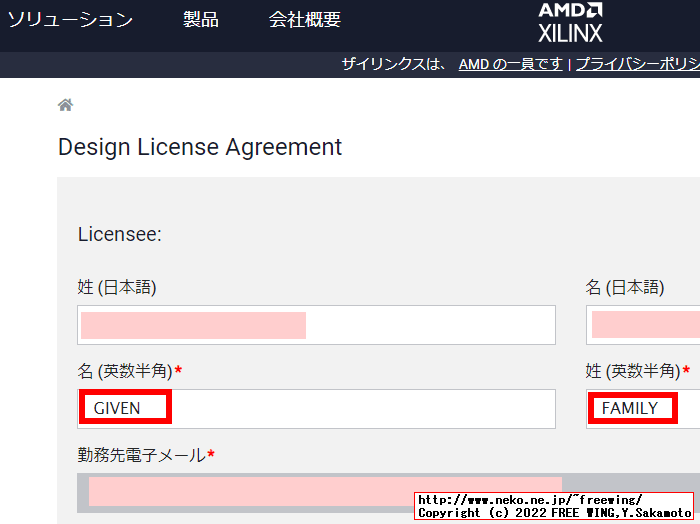

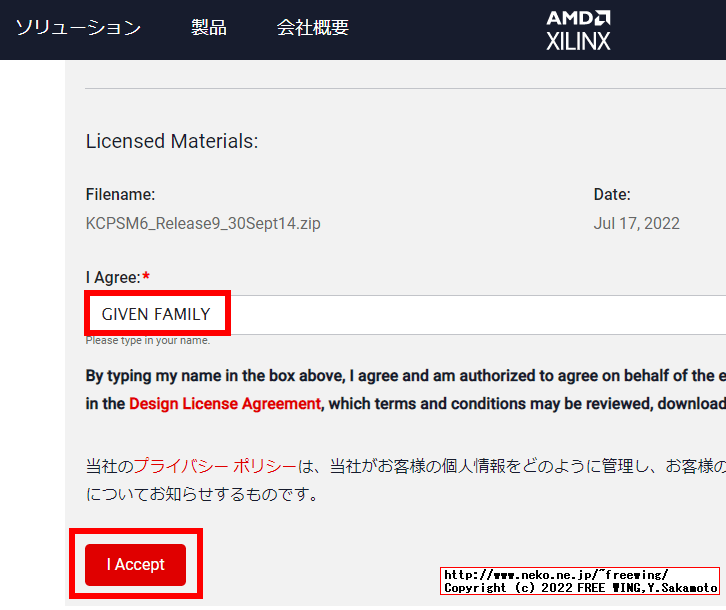

ダウンロードの際に I Agree欄に姓名を入力して、I Acceptボタンを押すとダウンロードが開始します。

ダウンロードの際に I Agree欄に姓名を入力して、I Acceptボタンを押すとダウンロードが開始します。

● Xilinxの FPGA Spartan-6で PicoBlazeのサンプルを ALINX AX309で動かす!

UART_and_PicoTermの 4桁の 16進数を 10進数に変換する UART通信のサンプルが動いたよ!

とりあえず大変でした。(説明書を読まないでいきなり動かそうとするから)

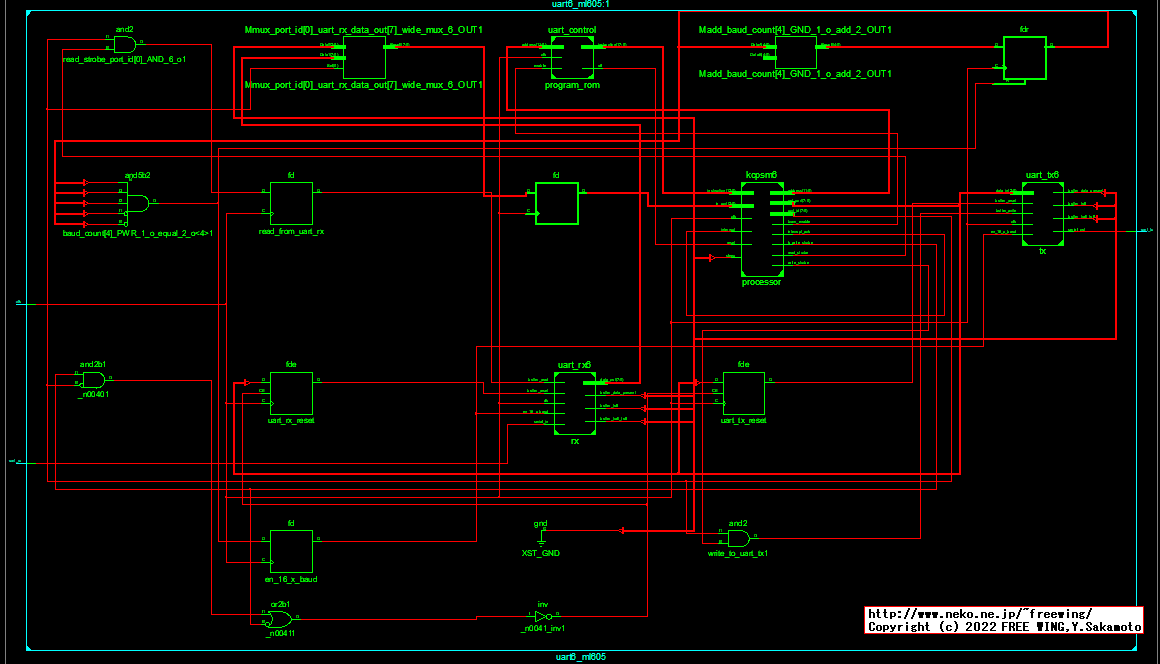

ML605_designを元にして ALINX AX309で動く様に基板の差異の部分を変更しました。

Virtex-6 FPGA ML605基板と ALINX AX309基板の差異の部分

| 差異の部分 | ML605基板 | AX309基板 | 対応方法 |

| 使用している FPGAが違う | Virtex-6 | Spartan-6 | JTAG Loaderの FPGAの定義を変更 |

| クロック源の仕様が違う | 差動クロック入力 | シングルエンド入力 | シングルエンド入力に変更する |

| クロックの周波数が違う | 200MHz | 50MHz | 50MHzをそのまま使う |

| UARTの I/Oのピン配置 | Tx=J25、Rx=J24 | Tx=D12、Rx=C11 | .ucfファイルを書き換える |

● uart6_ax309.ucf

AX309の基板の I/O配線で .ucfファイルの内容を変更して対応した。

クロック入力と USB UART通信。

uart6_ax309.ucf

#

# Period constraint for 50MHz operation

#

NET "clk50" LOC = T8 | TNM_NET = sys_clk_pin;

TIMESPEC TS_sys_clk_pin = PERIOD sys_clk_pin 50000 kHz;

#

# USB-UART

#

NET "uart_rx" LOC = "C11" | IOSTANDARD = LVCMOS33;

NET "uart_tx" LOC = "D12" | IOSTANDARD = LVCMOS33;

● uart6_ml605.v

ML605は 200MHzを 50MHzに変換する回路が有ったので、AX309の場合は入力の 50MHzをそのまま使う様にしただけで済んだ。

uart6_ml605.v

差動入力の 200MHzのピン定義を削除、clk50を追加

module uart6_ml605 ( input uart_rx,

// input clk200_p,

// input clk200_n,

input clk50,

output uart_tx );

...

// wire clk200;

wire clk;

ディファレンシャル入力回路と 200MHzを 50MHzに変換する回路をゴッソリ削除

/////////////////////////////////////////////////////////////////////////////////////////

// Create 50MHz clock from 200MHz differential clock

/////////////////////////////////////////////////////////////////////////////////////////

// IBUFGDS diff_clk_buffer(

// .I(clk200_p),

// .IB(clk200_n),

// .O(clk200));

// BUFR used to divide by 4 and create a regional clock

// BUFR #(

// .BUFR_DIVIDE("4"),

// .SIM_DEVICE("VIRTEX6"))

// clock_divide (

// .I(clk200),

// .O(clk),

// .CE(1'b1),

// .CLR(1'b0));

assign clk = clk50;

...

JTAG Loaderの FPGAの定義を Virtex-6から Spartan-6に変更

uart_controlの C_FAMILYを "V6"から "S6"、C_RAM_SIZE_KWORDSを 1から 2に変更する

// Development Program Memory

// JTAG Loader enabled for rapid code development.

uart_control #(

// .C_FAMILY ("V6"),

// .C_RAM_SIZE_KWORDS (2),

.C_FAMILY ("S6"),

.C_RAM_SIZE_KWORDS (1),

● PicoBlazeの .psmファイルをアセンブルして ROMファイルを生成する方法

プログラムの内容を格納する為の ROM_form.vテンプレートファイルが必要です。

UART_and_PicoTermの場合は Verilog言語で記述されており、JTAG Loader機能を使用しています。

.\KCPSM6_Release9_30Sept14\Verilog

の

ROM_form_JTAGLoader_3Mar11.v

ファイルを

ROM_form.v

のファイル名でコピーします。

この状態で uart_control.psmファイルをアセンブルすると、プログラムの内容が埋め込まれた uart_control.vファイルが生成されます。

・Xilinxの FPGA Spartan-6で PicoBlaze 8 ビット マイクロコントローラーを動かす!

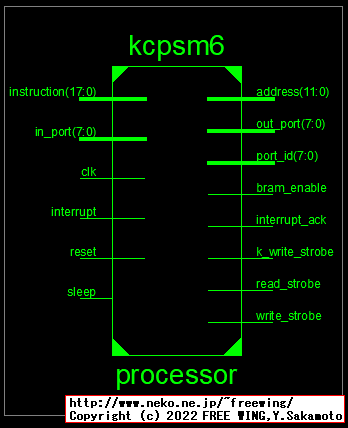

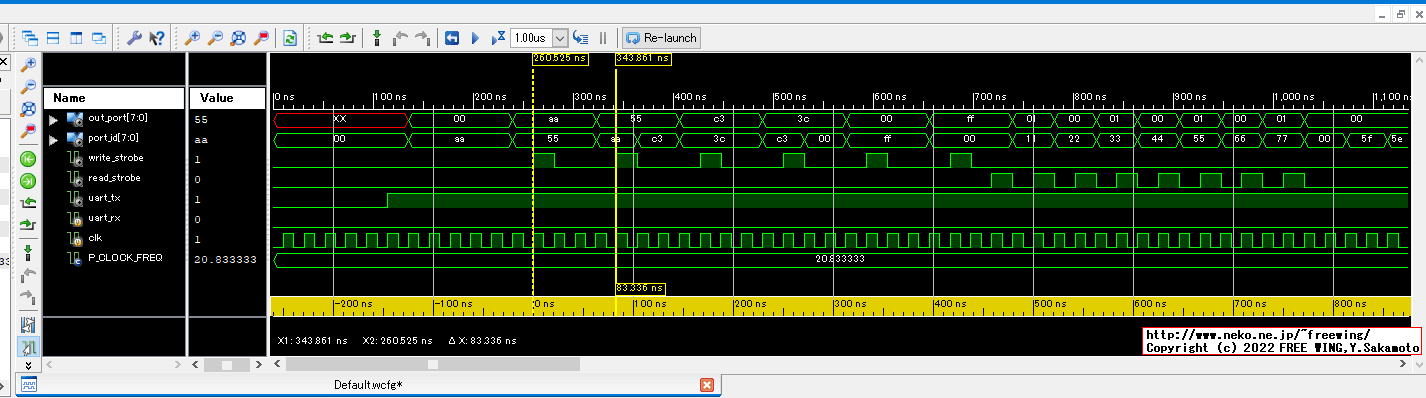

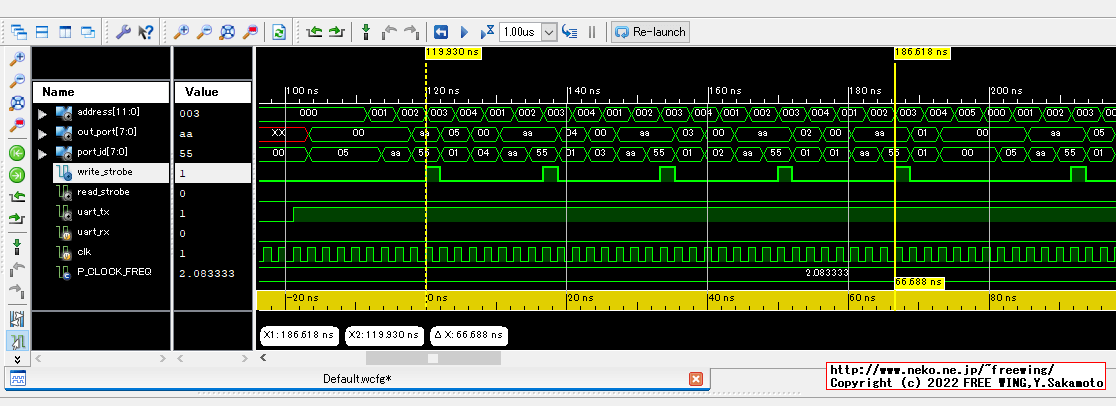

● PicoBlazeの I/Oポートのアクセスの動作仕様の調査

PicoBlazeは 1cycle = 2clockで動き、1命令を 1cycleで実行します。

48MHzで動作させた場合、16命令毎に USBの 1bitを送受信すれば 1.5Mbpsにできます。

1bit = 66.67ns= 48MHz / (2 * 16)

下記の移植の事前準備として調査しました。

・2022/07/17

USBの通信プロトコルを勉強する

今まで漠然としていた USBデバイスの通信方法を理解します

・2022/07/23

USB HOST機能を FPGAに実装する方法、FPGAの GPIOに USB HIDデバイスを接続したい!!

FPGAに USB HOST機能を実装して Low Speedの USB HIDデバイスを接続するのら

LOAD s5, AA

OUTPUT s5, 55

LOAD s5, 55

OUTPUT s5, AA

LOAD s5, C3

OUTPUT s5, 3C

LOAD s5, 3C

OUTPUT s5, C3

LOAD s5, 00

OUTPUT s5, FF

LOAD s5, FF

OUTPUT s5, 00

INPUT s5, 00

INPUT s5, 11

INPUT s5, 22

INPUT s5, 33

INPUT s5, 44

INPUT s5, 55

INPUT s5, 66

INPUT s5, 77

・PicoBlazeの I/Oポートのアクセスの動作仕様の確認

cold_start:

LOAD s0, 05

loop_x:

LOAD s5, AA

OUTPUT s5, 55

SUB s0, 1'd

JUMP NZ, loop_x

JUMP cold_start

・PicoBlazeの I/Oポートのアクセスの動作仕様の確認

● PicoBlaze KCPSMの JTAG Loaderの使用方法

jtagloader -l hoge\your_program.hex

● JTAG_Loader実行時に libCseJtag.dllが見つからない

JTAG_Loader_Win7_64.exeの JTAG_Loader実行時に libCseJtag.dllが見つからない。

解決方法: Startメニューの Xilinxの中のコマンドラインを実行し、その中から JTAG_Loader_Win7_64.exeを実行する。

●下記は大昔の Spartan-2時代の PicoBlazeの記事

もう記憶が無い。

でも、ソースリストを残しておいて偉いぞ!>俺

・2003/01/07

KCPSM-CPUコア(PicoBlaze)の実験

Ken Chapman氏作の芸術的CPU core

Tags: [FPGA], [電子工作], [Xilinx XC6SLX9], [FPGA 2022]

●関連するコンテンツ(この記事を読んだ人は、次の記事も読んでいます)

AMD Xilinxの FPGA Spartan-6 XC6SLX16のボードを買ってアーケード ゲームを動かす

ALINX AX309 XC6SLX9の中華クローンの XC6SLX16版を購入しました

AMD Xilinxの FPGAの開発アプリ ISE WebPackをダウンロードして Windows 10で動かす方法

Spartan-6の FPGAの開発用に Xilinx ISE WebPack開発ソフトウェアを Windows 10で動かす方法

Xilinxの FPGA Spartan-6の Block RAM RAMB8BWERに初期値を入れて ROMとして使う方法

Xilinxの FPGA Spartan-6の Block RAM RAMB8BWERに初期値を入れて ROMとして使う方法

FPGA Spartan-6 XC6SLX16でファミコンを動かす!

Xilinx FPGA Spartan-6 XC6SLX16 NES clone in ALINX AX309

Xilinxの FPGA Spartan-6で MicroBlazeを ISE WebPack 14.7で無料ライセンスで動かす方法

How to MicroBlaze in Spartan-6 with ISE WebPack 14.7 only Free License to Blink LED !

USB HOST機能を FPGAに実装する方法、FPGAの GPIOに USB HIDデバイスを接続したい!!

FPGAに USB HOST機能を実装して Low Speedの USB HIDデバイスを接続するのら

USBの通信プロトコルを勉強する

今まで漠然としていた USBデバイスの通信方法を理解します

USB HOST機能が欲しいのでワンチップマイコンの GPIOで USB HOST機能を実現する

FPGAに USBデバイスを接続したいのですが、USB HOSTの通信を実装できないので困っています

OLIMEX LPC-H40(Philips LPC2106)

MOTHER BOARD for LPC-H40(LPC-H2106) and ASM Sample Program.

線形帰還シフトレジスタ LFSRのまとめ、FPGAの Verilog HDLでの実装例

LFSR Linear Feedback Shift Registerについて調べた

【2022年版】最近流行の RISC-Vプロセッサの環境を WSL Ubuntu上に構築する方法

RISC-Vプロセッサの Rocket Chipの開発環境を Windows上に構築して Verilogする方法

XILINX FPGAのBlock RAMをROMとして使う方法

FPGAに内蔵のBLOCK-RAMにROMとして初期値を与える方法

スパルタン2で"ギャラクシアン基板"を作る!

Verilog言語で記述してあります

スパルタン2で"MIDWAY 8080(TAITO インベーダ基板)"を動かす!

ハードウェアで本物を作ります

スパルタン2で"パックマン"を動かす!

FPGAでパックマンが動きます

スパルタン2で"ド*キーコ*グ"を動かす!

これもFPGAで動いちゃいます

スパルタン3でアーケードゲームを動かす!

XAPP694の使用例、INVADER/GALAXIAN/PACMAN/D*NKEY-K*NG/TIME PILOT

[HOME]

|

[BACK]

リンクフリー(連絡不要、ただしトップページ以外は Web構成の変更で移動する場合があります)

Copyright (c)

2022 FREE WING,Y.Sakamoto

Powered by 猫屋敷工房 & HTML Generator

http://www.neko.ne.jp/~freewing/fpga/xilinx_spartan6_picoblaze/