|

|

|

|

FPGAプログラミング大全 Xilinx編 第2版 単行本 - 2021/1/30 ASIN: 4798063266 |

Verilog HDL&VHDLテストベンチ記述の初歩 (DESIGN WAVE MOOK) 単行本 - 2011/3/30 ASIN: 4789831086 |

PUの創りかた 単行本(ソフトカバー) - 2003/10/1 ASIN: 4839909865 |

RISC-VとChiselで学ぶ はじめてのCPU自作 ― オープンソース命令セットによるカスタムCPU実装への第一歩 単行本(ソフトカバー) - 2021/8/25 ASIN: 4297123053 |

| n(bit) | XOR from(tap) |

| 4 bit | 4、3 |

| 8 bit | 8、6、5、4 |

| 9 bit | 9、5 |

| 16 bit | 14、15、13、4 |

| 17 bit | 17、14 |

| 32 bit | 32、22、2、1 |

| 33 bit | 33、20 |

| 168 bit | 168、166、153、151 |

module lfsr (CLK, load, seed, out);

// port

input CLK;

input load;

input [7:0] seed;

output [7:0] out;

// internal

reg [7:0] r;

wire tmp_xor;

always @(posedge CLK) begin

if (load)

r <= seed;

else begin

r <= (r<<1) | tmp_xor;

end

end

// 8 bit tap 8,6,5,4

assign tmp_xor = r[7]^r[5]^r[4]^r[3];

assign out = r;

endmodule

module lfsr (CLK, load, seed, out);

// port

input CLK;

input load;

input [7:0] seed;

output [7:0] out;

// internal

reg [7:0] r;

always @(posedge CLK) begin

if (load)

r <= seed;

else begin

// 8 bit tap 8,6,5,4

r <= {r[0], r[7], r[0]^r[6], r[0]^r[5], r[0]^r[4], r[3], r[2], r[1]};

end

end

assign out = r;

endmodule

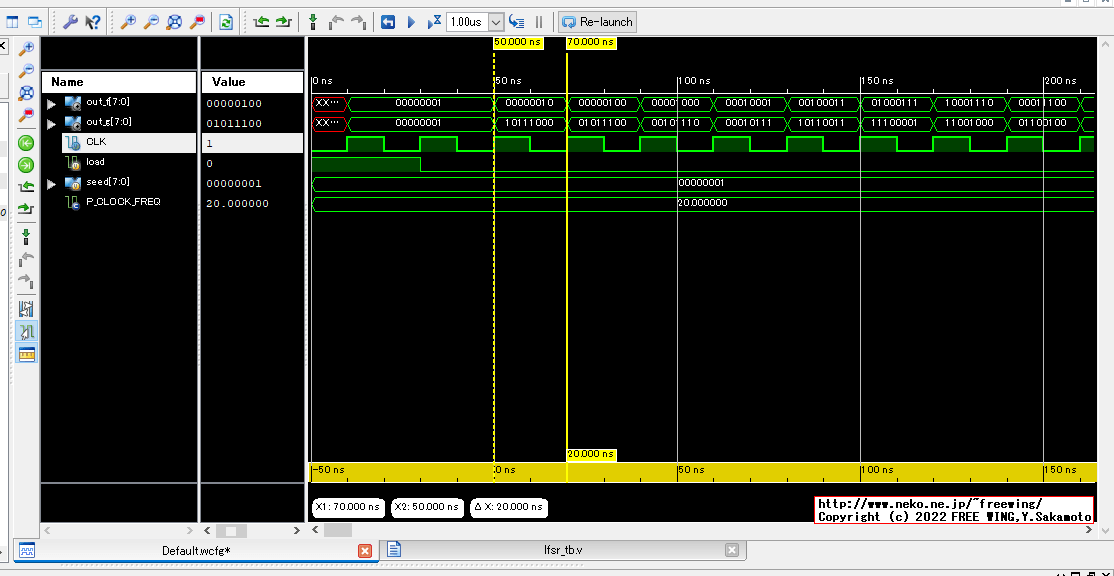

`timescale 1ns/100ps

`include "lfsr.v"

module lfsr_tb;

reg CLK;

wire load;

wire [7:0] seed;

wire [7:0] out;

lfsr uut(

.CLK (CLK),

.load (load),

.seed (seed),

.out (out[7:0])

);

parameter P_CLOCK_FREQ = 1000.0 / 50.0; // 50MHz

initial begin

CLK = 1'b0;

end

always #(P_CLOCK_FREQ/2) begin

CLK <= ~CLK;

end

initial begin

load = 1;

seed = 1;

repeat(2) @(posedge CLK);

load = 0;

end

initial begin

@(posedge CLK);

while(load) @(posedge CLK);

repeat(255 + 4) @(posedge CLK);

$finish;

end

endmodule

Fibonacci Galois xxxxxxxx xxxxxxxx 00000001 00000001 00000001 00000001 開始 1 00000010 10111000 2 00000100 01011100 3 00001000 00101110 4 00010001 00010111 ... 00100011 10110011 01000111 11100001 10001110 11001000 00011100 01100100 00111000 00110010 01110001 00011001 11100010 10110100 11000100 01011010 10001001 00101101 00010010 10101110 00100101 01010111 01001011 10010011 10010111 11110001 00101110 11000000 01011100 01100000 10111000 00110000 01110000 00011000 11100000 00001100 11000000 00000110 10000001 00000011 00000011 10111001 00000110 11100100 00001100 01110010 00011001 00111001 00110010 10100100 01100100 01010010 11001001 00101001 10010010 10101100 00100100 01010110 01001001 00101011 10010011 10101101 00100110 11101110 01001101 01110111 10011011 10000011 00110111 11111001 01101110 11000100 11011100 01100010 10111001 00110001 01110010 10100000 11100100 01010000 11001000 00101000 10010000 00010100 00100000 00001010 01000001 00000101 10000010 10111010 00000101 01011101 00001010 10010110 00010101 01001011 00101011 10011101 01010110 11110110 10101101 01111011 01011011 10000101 10110110 11111010 01101101 01111101 11011010 10000110 10110101 01000011 01101011 10011001 11010110 11110100 10101100 01111010 01011001 00111101 10110010 10100110 01100101 01010011 11001011 10010001 10010110 11110000 00101100 01111000 01011000 00111100 10110000 00011110 01100001 00001111 11000011 10111111 10000111 11100111 00001111 11001011 00011111 11011101 00111110 11010110 01111101 01101011 11111011 10001101 11110110 11111110 11101101 01111111 11011011 10000111 10110111 11111011 01101111 11000101 11011110 11011010 10111101 01101101 01111010 10001110 11110101 01000111 11101011 10011011 11010111 11110101 10101110 11000010 01011101 01100001 10111010 10001000 01110100 01000100 11101000 00100010 11010001 00010001 10100010 10110000 01000100 01011000 10001000 00101100 00010000 00010110 00100001 00001011 01000011 10111101 10000110 11100110 00001101 01110011 00011011 10000001 00110110 11111000 01101100 01111100 11011000 00111110 10110001 00011111 01100011 10110111 11000111 11100011 10001111 11001001 00011110 11011100 00111100 01101110 01111001 00110111 11110011 10100011 11100111 11101001 11001110 11001100 10011100 01100110 00111001 00110011 01110011 10100001 11100110 11101000 11001100 01110100 10011000 00111010 00110001 00011101 01100010 10110110 11000101 01011011 10001011 10010101 00010110 11110010 00101101 01111001 01011010 10000100 10110100 01000010 01101001 00100001 11010010 10101000 10100100 01010100 01001000 00101010 10010001 00010101 00100010 10110010 01000101 01011001 10001010 10010100 00010100 01001010 00101001 00100101 01010010 10101010 10100101 01010101 01001010 10010010 10010101 01001001 00101010 10011100 01010100 01001110 10101001 00100111 01010011 10101011 10100111 11101101 01001110 11001110 10011101 01100111 00111011 10001011 01110111 11111101 11101110 11000110 11011101 01100011 10111011 10001001 01110110 11111100 11101100 01111110 11011001 00111111 10110011 10100111 01100111 11101011 11001111 11001101 10011110 11011110 00111101 01101111 01111011 10001111 11110111 11111111 11101111 11000111 11011111 11011011 10111111 11010101 01111110 11010010 11111101 01101001 11111010 10001100 11110100 01000110 11101001 00100011 11010011 10101001 10100110 11101100 01001100 01110110 10011001 00111011 00110011 10100101 01100110 11101010 11001101 01110101 10011010 10000010 00110101 01000001 01101010 10011000 11010100 01001100 10101000 00100110 01010001 00010011 10100011 10110001 01000110 11100000 10001100 01110000 00011000 00111000 00110000 00011100 01100000 00001110 11000001 00000111 10000011 10111011 00000111 11100101 00001110 11001010 00011101 01100101 00111010 10001010 01110101 01000101 11101010 10011010 11010101 01001101 10101010 10011110 01010101 01001111 10101011 10011111 01010111 11110111 10101111 11000011 01011111 11011001 10111110 11010100 01111100 01101010 11111001 00110101 11110010 10100010 11100101 01010001 11001010 10010000 10010100 01001000 00101000 00100100 01010000 00010010 10100001 00001001 01000010 10111100 10000100 01011110 00001001 00101111 00010011 10101111 00100111 11101111 01001111 11001111 10011111 11011111 00111111 11010111 01111111 11010011 11111111 11010001 11111110 11010000 11111100 01101000 11111000 00110100 11110000 00011010 11100001 00001101 11000010 10111110 10000101 01011111 00001011 10010111 00010111 11110011 00101111 11000001 01011110 11011000 10111100 01101100 01111000 00110110 11110001 00011011 11100011 10110101 11000110 11100010 10001101 01110001 00011010 10000000 00110100 01000000 01101000 00100000 11010000 00010000 ... 10100000 00001000 253 01000000 00000100 254 10000000 00000010 255 00000001 00000001 ここで1週 256 00000010 10111000 257 00000100 01011100 258 00001000 00101110 ... 00010001 00010111