・2004/07/06

16bit CPU-coreの実験(C-NIT)

16bit CPU-coreの実験(C-NIT)

(SD-RAM対応の高性能CPU core)

Tags: [FPGA], [電子工作]

16bit CPU-coreを動かします。

SD-RAMコントローラを内蔵で外部記憶としてSD-RAMが使用できます(約64kbyte空間)

また、SD-RAMのアクセスを稼ぐ為に内部BLOCK-RAMをキャッシュメモリとして使用しています。

これだけの機能があって使用スライスはたったの380sliceです。

使用素材

・

C-NIT is a 16 bit RISC processor

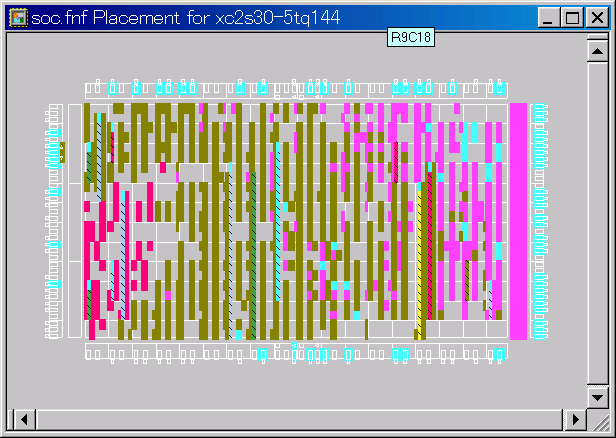

CPUコアの内部使用率

XC2S30

Release 4.2WP3.x - Par E.38

Device utilization summary:

Number of External GCLKIOBs 1 out of 4 25%

Number of External IOBs 58 out of 92 63%

Number of LOCed External IOBs 0 out of 58 0%

Number of BLOCKRAMs 3 out of 6 50%

Number of SLICEs 380 out of 432 87%

Number of GCLKs 1 out of 4 25%

Number of TBUFs 104 out of 480 21%

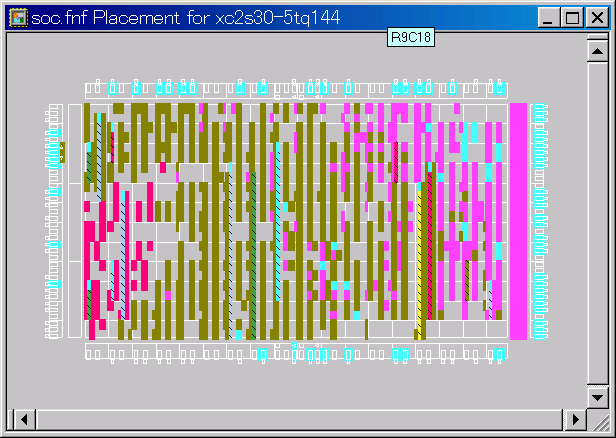

ソースリストに手を入れてロジックを最適化して、消費スライスを22減らしました。

Release 4.2WP3.x - Par E.38

Device utilization summary:

Number of External GCLKIOBs 1 out of 4 25%

Number of External IOBs 58 out of 92 63%

Number of LOCed External IOBs 0 out of 58 0%

Number of BLOCKRAMs 3 out of 10 30%

Number of SLICEs 358 out of 1200 29%

Number of GCLKs 1 out of 4 25%

Number of TBUFs 104 out of 1280 8%

Tags: [FPGA], [電子工作]

●関連するコンテンツ(この記事を読んだ人は、次の記事も読んでいます)

PIC16C57互換のIP-coreの実験

FPGAの中にCPU coreを組み込む

KCPSM-CPUコア(PicoBlaze)の実験

Ken Chapman氏作の芸術的CPU core

ヒューマンデータ製 ALTERA Cycloneボード

AlteraのCycloneは高性能

スパルタン2ってな~に?

簡単な紹介

スパルタン3でアーケードゲームを動かす!

XAPP694の使用例、INVADER/GALAXIAN/PACMAN/D*NKEY-K*NG/TIME PILOT

[HOME]

|

[BACK]

リンクフリー(連絡不要、ただしトップページ以外は Web構成の変更で移動する場合があります)

Copyright (c)

2004 FREE WING,Y.Sakamoto

Powered by 猫屋敷工房 & HTML Generator

http://www.neko.ne.jp/~freewing/fpga/cpu_cnit/