・2004/08/09

FPGA TIPs

(開発中に疑問に思った事の解決方法)

Tags: [FPGA], [電子工作]

ザイリンクスホットラインに実際に問い合わせをした内容と解決方法を順次まとめていきます。

青色はザイリンクスホットラインの回答部分です。

※私が独自に調べたものもあります。

※無保証です。

04/08/09

・iMPACTが鬼のように使いにくい、と言うか操作が非常に面倒(特にISE6.x以降)

特に、XAPP694の

「Reading User Data from Configuration PROMs」

を行なう場合など、

数回デバグしただけで、「もう嫌じゃー!」状態になってしまいます。

(毎回毎回かったるいマウス操作に耐えられますか?)

なので、私の場合はbit->MCS変換&ユーザーデータ混合ツールを作ってしまいました。(非公開)

※さとうさんのSPCISP

を参考にして作りました。

MCSファイルを作成した後は実際にコンフィグROMに書き込みですが、これもマウス操作だと苦痛を伴います。

それで、思い出したのですが、iMPACTにはマウス操作のGUIモードと

コマンドラインで操作のBATCHモードがあります。

下記アーカイブは「コンフィグROMに書き込み」を行うバッチファイルが入っています。

1クリックでプログラミングのバッチファイル

これを適当に改造して使いましょう。

※bit->MCS変換は単なるインテルHEXですのでiMPACTを使わずとも簡単にツールを自作できると思います。

・FPGA/CPLDが上手く動いてくれない

チェックポイント:

・INPUT端子に正しくPULL-UP指定をしているかどうか。(必要な場合)

・BIDIR(双方向)端子が正しくBIDIRとしてコンパイルされているかどうか。

(UCFエディタで確認できます。)

・UCFファイルを読み込んで、端子が正しく割り当てられているかどうか。

(UCFエディタで確認できます。)

・とりあえずModelSimで波形を確認する。

・入力信号のピン番号割り当てでクロック信号と自動認識することによるMAPエラーの回避方法

>・XC2S100-TQ144-5C

>・Verilog+SCH設計

>・WebISE-4.1WP2.0

>・XST

>

>添付ファイルのプロジェクト"I2C_S.npl"において、トップ階層の

>"i2c_top.sch"に対してピン番号割り当て"i2c_top.ucf"を行っているの

>ですが、MAPの時に下記のエラーが出てしまいます。

>

>

>Release 4.1WP2.x - Map E.32

>Copyright (c) 1995-2001 Xilinx, Inc. All rights reserved.

>Using target part "2s100tq144-5".

>ERROR:MapLib:93 - Illegal LOC on symbol "SCLK" (pad signal=SCLK)

>or BUFGP symbol

> "SCLK_BUFGP" (output signal=SCLK_BUFGP), IPAD-IBUFG should

>only be LOCed to

> GCLKIOB site.

>

>信号名"SCLK"に対してGCLKIOBの所しかピン番号定義はできないと言って

>いると思うのですが、USELOWSKEWLINES、MAXSKEW定義を追加してもエラ

>ーがでてしまいます。

>

>【質問1】何とかSCLKを"P20"にする方法はないのでしょうか?

>(なお、"CIN"は"P18","SDATBI"は"P19"等、UCFで設定しているその他の

>ピンもピン位置絶対条件です。)

この問題は内部でクロックとして使用されているネットに対し、

合成ツールが自動で BUFG を使用してしまうために起こるものです。

SCLK 入力パッドから i2c_s のクロック入力までの間に "IBUF"

コンポーネントを挿入してお試しください。

>【質問2】WebISEが自動的にグローバルクロックの必要性を類推

>して割り当てると思うのですが、("CIN","SCLK","SDATBI","WE")これ

>らの自動類推を抑制する方法はあるのでしょうか?

>(ユーザー側で明示的に手動で設定したい場合)

こちらも、上記の方法で回避していただけます。

以上よろしくお願いいたします。

XILINX JHOTLINE

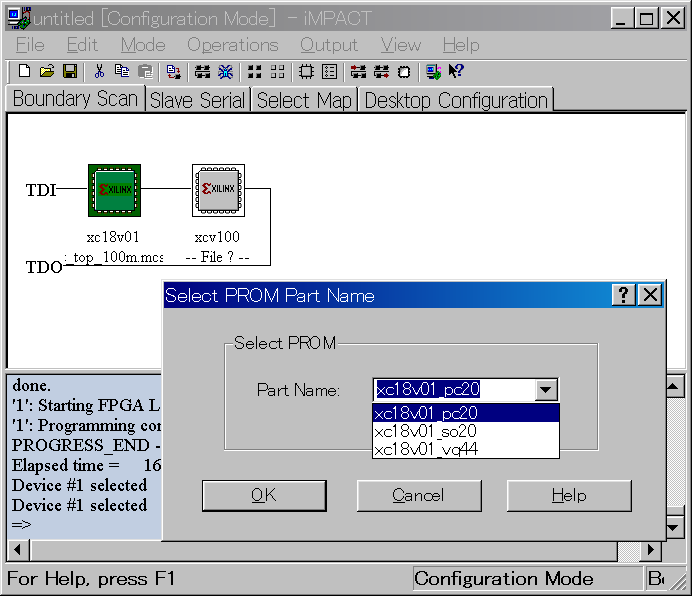

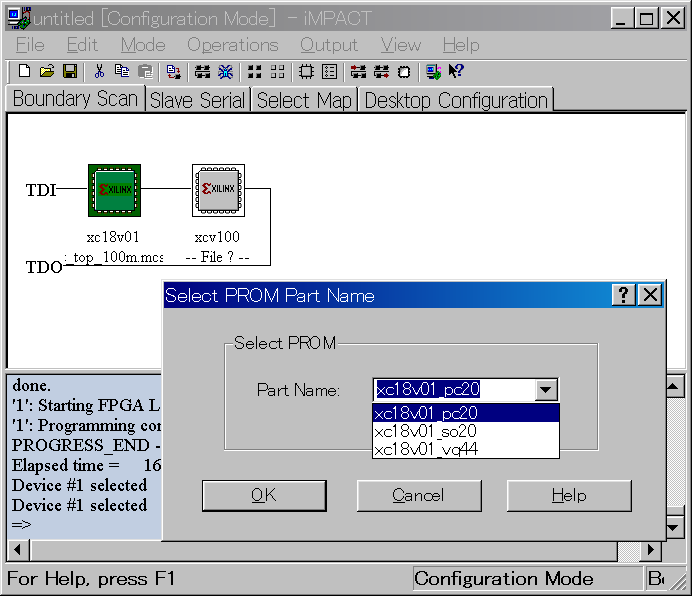

・IMPACTでコンフィグROMのファイルを読み込んだ時にデバイス種別を選ぶ必要性

例えばXC18V01は下記3タイプのパッケージが存在します。

結論から言うと実際に書き込むパッケージ形状がPLCC20の場合でも"pc20"を選ぶ必要はありません。

同じようにSOP20の場合でも"so20"を選ぶ必要はありません。

"XC18V01"が合っていればどれでもOKです。

結論から言うと実際に書き込むパッケージ形状がPLCC20の場合でも"pc20"を選ぶ必要はありません。

同じようにSOP20の場合でも"so20"を選ぶ必要はありません。

"XC18V01"が合っていればどれでもOKです。

・FPGA/CPLDで+5Vを駆動する方法(相手が+5V系C-MOSの場合)

結論から言うと外部にプルアップ抵抗が必要です。(参考値:10kΩ)

FPGA/CPLDの出力端子を+5V系C-MOSに接続する場合、

'H'レベルが+5Vの70%(+3.5V)以上必要になります。

大抵はC-MOS側入力にマージンがあるため+3.3V出力でそのまま動いてくれますが、

好ましくありません。

そこで、FPGA/CPLD側の出力をオープンドレインにしてプルアップ抵抗を付ける訳ですが、

'H'に変化する時に波形がなまります。

そこで、ザイリンクスではフィードバックループを推奨しています。

+3.3V から +5V を駆動する方法 (オープン ドレイン)

ソリューション 2:

フィードバックループを使用すると、トライステートになって外部プルアップ抵抗が

使用されるまでの短時間、出力で最高 3.3V (または 2.5V) まで駆動できます。

この方法には、ソリューション 1 に比べて、0V から 3.3V (または 2.5V) に

上昇する時間が早くなるという利点があります。

ソリューション 2:

フィードバックループを使用すると、トライステートになって外部プルアップ抵抗が

使用されるまでの短時間、出力で最高 3.3V (または 2.5V) まで駆動できます。

この方法には、ソリューション 1 に比べて、0V から 3.3V (または 2.5V) に

上昇する時間が早くなるという利点があります。

・ModelSim -- ERROR: "Too many port connections - fatal error."

ModelSim で シミュレーションを行なう時に、

*Simulate Post-Translate Verilog Model

ではエラー無くシミュレーションが実行できますが、

*Simulate PostーPlace & Route Verilog Model

では、"Too many port connections - fatal error."のエラーが出てしまいます。

テスト回路では、わざとAND入力の片側をGNDに固定して回路的に無意味にしていますが、

ザイリンクスの最適化によって取り去られてしまい、

それでModelSimでは、「該当の端子が無い」とエラーを出すものと思います。

この、

*Simulate PostーPlace & Route Verilog Model

でエラーが出ないように、最適化を抑制する事は可能でしょうか?

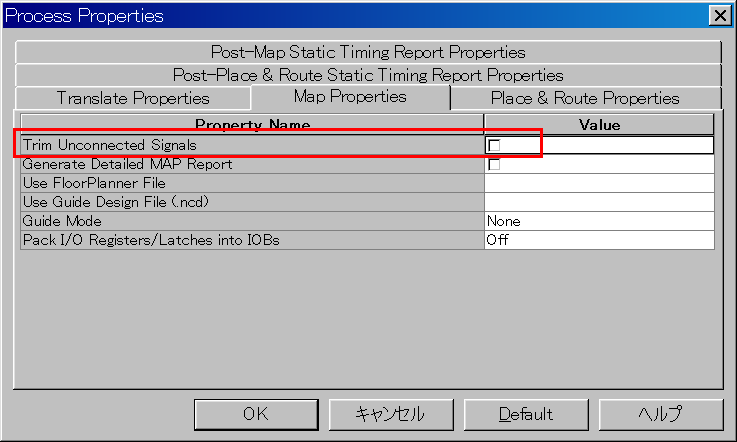

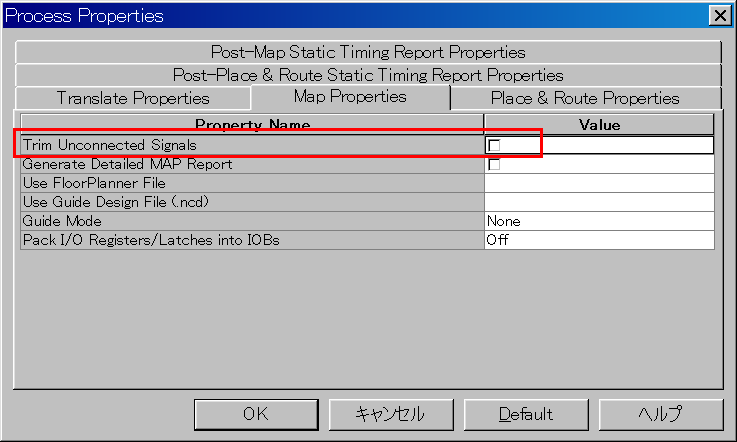

Implement Design -> Map -> Trim Unconnected Signalsの チェックをオフにしてください。

これによりネットが削除されなくなります。

Xilinx Jhotline

※Windows 2000 SP3 で起動時ハングアップの場合の対策

WebPACK-ISE 4.2i Install - Windows 2000 Service Pack 3

・Z80 IP-core のゲート使用率について。

Release 4.2WP3.x - Par E.38

Copyright (c) 1995-2001 Xilinx, Inc. All rights reserved.

・

Project: T80 cpu (OPENCORES.ORG)

device xc2s150, package pq208, speed -5

Device utilization summary:

Number of External GCLKIOBs 1 out of 4 25%

Number of External IOBs 46 out of 140 32%

Number of LOCed External IOBs 0 out of 46 0%

Number of SLICEs 1208 out of 1728 69%

Number of GCLKs 1 out of 4 25%

Overall effort level (-ol): 2 (set by user)

Placer effort level (-pl): 2 (set by user)

Placer cost table entry (-t): 1

Router effort level (-rl): 2 (set by user)

Extra effort level (-xe): 0 (set by user)

・

Z80CPU互換IP (FPGA インフォメーション)

device xc2s100, package tq144, speed -5

Device utilization summary:

Number of External GCLKIOBs 1 out of 4 25%

Number of External IOBs 43 out of 92 46%

Number of LOCed External IOBs 0 out of 43 0%

Number of SLICEs 965 out of 1200 80%

Number of GCLKs 1 out of 4 25%

Overall effort level (-ol): Not applicable because -pl and -rl switches are used

Placer effort level (-pl): 5 (set by user)

Placer cost table entry (-t): 1

Router effort level (-rl): 5 (set by user)

Extra effort level (-xe): 2 (set by user)

・

FZ80 (FPGAでPC-8001を作る計画)

750 SLICEs位

・以下編集中

Tags: [FPGA], [電子工作]

●関連するコンテンツ(この記事を読んだ人は、次の記事も読んでいます)

ヒューマンデータ製 ALTERA Cycloneボード

AlteraのCycloneは高性能

スパルタン2ってな~に?

簡単な紹介

スパルタン3でアーケードゲームを動かす!

XAPP694の使用例、INVADER/GALAXIAN/PACMAN/D*NKEY-K*NG/TIME PILOT

Altera/Xilinxの FPGA機能一覧表

PDFで調べるのが面倒な時に

Xilinx用便利ソフトのダウンロード

Xilinx WebPACK-ISE用

[HOME]

|

[BACK]

リンクフリー(連絡不要、ただしトップページ以外は Web構成の変更で移動する場合があります)

Copyright (c)

2002-2003 FREE WING,Y.Sakamoto

Powered by 猫屋敷工房 & HTML Generator

http://www.neko.ne.jp/~freewing/fpga/fpga_tips/

結論から言うと実際に書き込むパッケージ形状がPLCC20の場合でも"pc20"を選ぶ必要はありません。

同じようにSOP20の場合でも"so20"を選ぶ必要はありません。

"XC18V01"が合っていればどれでもOKです。

結論から言うと実際に書き込むパッケージ形状がPLCC20の場合でも"pc20"を選ぶ必要はありません。

同じようにSOP20の場合でも"so20"を選ぶ必要はありません。

"XC18V01"が合っていればどれでもOKです。

結論から言うと実際に書き込むパッケージ形状がPLCC20の場合でも"pc20"を選ぶ必要はありません。 同じようにSOP20の場合でも"so20"を選ぶ必要はありません。 "XC18V01"が合っていればどれでもOKです。

ソリューション 2: フィードバックループを使用すると、トライステートになって外部プルアップ抵抗が 使用されるまでの短時間、出力で最高 3.3V (または 2.5V) まで駆動できます。 この方法には、ソリューション 1 に比べて、0V から 3.3V (または 2.5V) に 上昇する時間が早くなるという利点があります。